1T-SRAM

This article includes a list of references, related reading, or external links, but its sources remain unclear because it lacks inline citations. (December 2012) |

| Computer memory and data storage types |

|---|

| Volatile |

| Non-volatile |

1T-SRAM is a pseudo-static random-access memory (PSRAM) technology introduced by MoSys, Inc. in September 1998, which offers a high-density alternative to traditional static random-access memory (SRAM) in embedded memory applications. Mosys uses a single-transistor storage cell (bit cell) like dynamic random-access memory (DRAM), but surrounds the bit cell with control circuitry that makes the memory functionally equivalent to SRAM (the controller hides all DRAM-specific operations such as precharging and refresh). 1T-SRAM (and PSRAM in general) has a standard single-cycle SRAM interface and appears to the surrounding logic just as an SRAM would.

Due to its one-transistor bit cell, 1T-SRAM is smaller than conventional (six-transistor, or "6T") SRAM, and closer in size and density to embedded DRAM (eDRAM). At the same time, 1T-SRAM has performance comparable to SRAM at multi-megabit densities, uses less power than eDRAM and is manufactured in a standard CMOS logic process like conventional SRAM.

MoSys markets 1T-SRAM as physical IP for embedded (on-die) use in System-on-a-chip (SOC) applications. It is available on a variety of foundry processes, including Chartered, SMIC, TSMC, and UMC. Some engineers use the terms 1T-SRAM and "embedded DRAM" interchangeably, as some foundries provide MoSys's 1T-SRAM as "eDRAM". However, other foundries provide 1T-SRAM as a distinct offering.

Technology

[edit]1T SRAM is built as an array of small banks (typically 128 rows × 256 bits/row, 32 kilobits in total) coupled to a bank-sized SRAM cache and an intelligent controller. Although space-inefficient compared to regular DRAM, the short word lines allow much higher speeds, so the array can do a full sense and precharge (RAS cycle) per access, providing high-speed random access. Each access is to one bank, allowing unused banks to be refreshed at the same time. Additionally, each row read out of the active bank is copied to the bank-sized SRAM cache. In the event of repeated accesses to one bank, which would not allow time for refresh cycles, there are two options: either the accesses are all to different rows, in which case all rows will be refreshed automatically, or some rows are accessed repeatedly. In the latter case, the cache provides the data and allows time for an unused row of the active bank to be refreshed.

There have been four generations of 1T-SRAM:[when?]

- Original 1T-SRAM

- About half the size of 6T-SRAM, less than half the power.

- 1T-SRAM-M

- Variant with lower standby power consumption, for applications such as cell phones.

- 1T-SRAM-R

- Incorporates ECC for lower soft error rates. To avoid an area penalty, it uses smaller bit cells, which have an inherently higher error rate, but the ECC more than makes up for that.

- 1T-SRAM-Q

- This "quad-density" version uses a slightly non-standard fabrication process to produce a smaller folded capacitor, allowing the memory size to be halved again over 1T-SRAM-R. This does add slightly to wafer production costs, but does not interfere with logic transistor fabrication the way conventional DRAM capacitor construction does.

Comparison with other embedded memory technologies

[edit]1T-SRAM has speed comparable to 6T-SRAM (at multi-megabit densities). It is significantly faster speed than eDRAM, and the "quad-density" variant is only slightly larger (10–15% is claimed). On most foundry processes, designs with eDRAM require additional (and costly) masks and processing steps, offsetting the cost of a larger 1T-SRAM die. Also, some of those steps require very high temperatures and must take place after the logic transistors are formed, possibly damaging them.

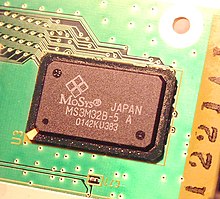

1T-SRAM is also available in device (IC) form. The GameCube was the first video game system to use 1T-SRAM as main memory storage; the GameCube possesses several dedicated 1T-SRAM devices. 1T-SRAM is also used in the successor to the GameCube, the Wii.

This is not the same as 1T DRAM, which is a "capacitorless" DRAM cell built using the parasitic channel capacitor of SOI transistors rather than a discrete capacitor.

MoSys claims the following sizes for 1T-SRAM arrays:

| Process node | 250 nm | 180 nm | 130 nm | 90 nm | 65 nm | 45 nm | |

|---|---|---|---|---|---|---|---|

| 6T-SRAM | bit cell | 7.56 | 4.65 | 2.43 | 1.36 | 0.71 | 0.34 |

| with overhead | 11.28 | 7.18 | 3.73 | 2.09 | 1.09 | 0.52 | |

| 1T-SRAM | bit cell | 3.51 | 1.97 | 1.10 | 0.61 | 0.32 | 0.15 |

| with overhead | 7.0 | 3.6 | 1.9 | 1.1 | 0.57 | 0.28 | |

| 1T-SRAM-Q | bit cell | 0.50 | 0.28 | 0.15 | 0.07 | ||

| with overhead | 1.05 | 0.55 | 0.29 | 0.14 | |||

See also

[edit]US Patent 7,146,454"Hiding refresh in 1T-SRAM Architecture"* (by Cypress Semiconductor) describes a similar system for hiding DRAM refresh using an SRAM cache.

References

[edit]- Glaskowsky, Peter N. (1999-09-13). "MoSys Explains 1T-SRAM Technology: Unique Architecture Hides Refresh, Makes DRAM Work Like SRAM" (PDF). Microprocessor Report. 13 (12). Retrieved 2007-10-06.

- Jones, Mark-Eric (2003-10-14). 1T-SRAM-Q: Quad-Density Technology Reins in Spiraling Memory Requirements (PDF) (Report). MoSys, Inc. Retrieved 2007-10-06.

- MoSys homepage

- US Patent 6,256,248 shows the DRAM array at the heart of 1T-SRAM.

- US Patent 6,487,135 uses the term "1T DRAM" to describe the innards of 1T-SRAM.

- Youths, Techfor (2002-12-16). "1-T SRAM macros are preconfigured for fast integration in SoC designs". Archived from the original on 2019-07-20. Retrieved 2020-08-21.

- Cataldo, Anthony (2002-12-16). "NEC, Mosys push bounds of embedded DRAM". EE Times. ISSN 0192-1541. Retrieved 2007-10-06.